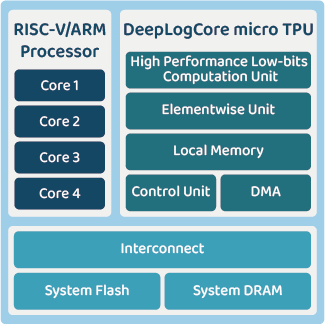

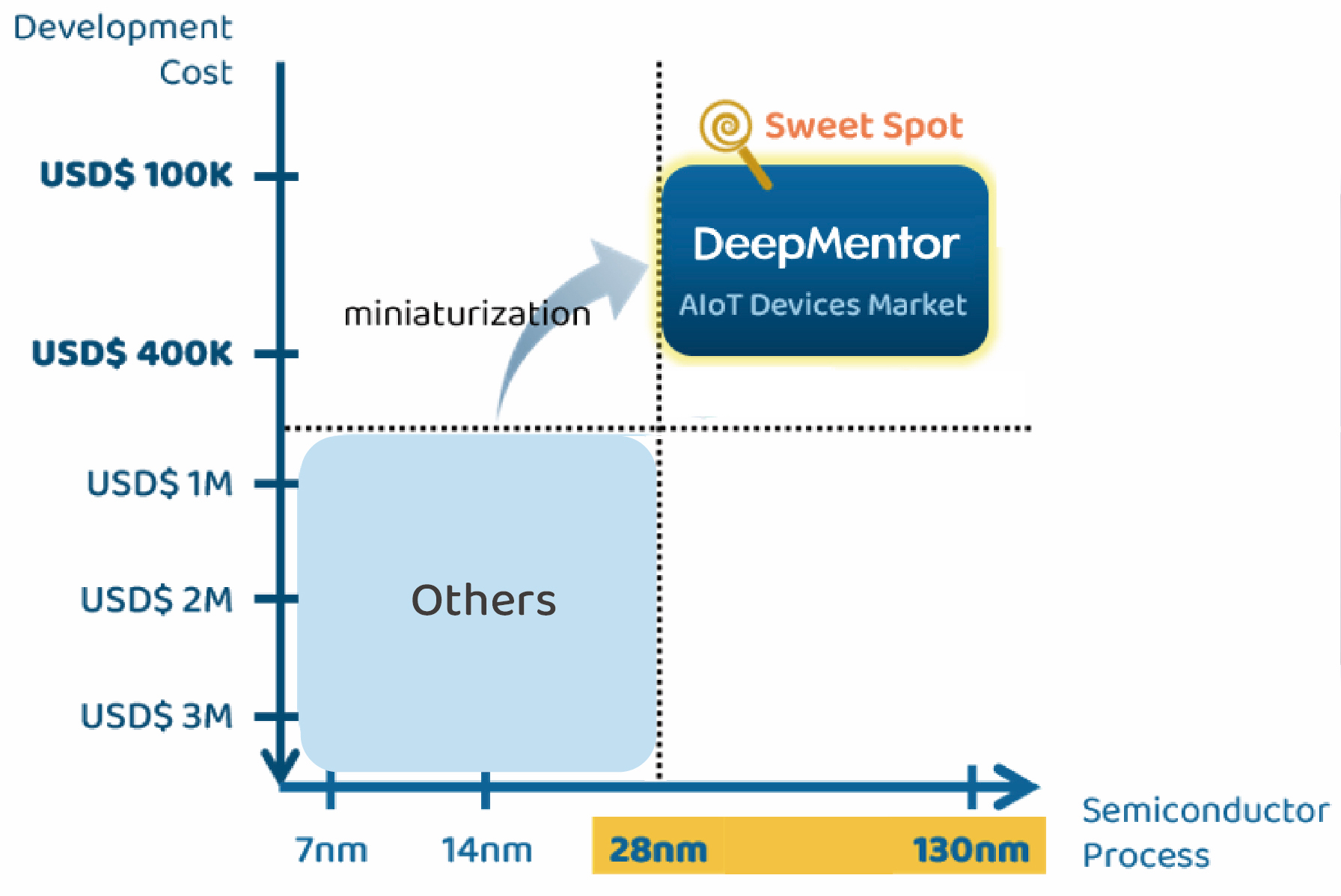

DeepLogcore is a soft AI IP compatible with a wide range of processes, particularly mature and power-saving low-cost processes between 28nm to 130nm. As a result, customers can control their manufacturing costs according to their specific needs and market demands.